Workshop on Architecture of Smart Camera

# Real-time Harris and Stephen implementation on Smart camera

Merwan BIREM François BERRY

5-6 April 2012 Clermont-Ferrand, FRANCE

# Summary

- I Feature Extraction,

- 2 Harris & Stephen detector,

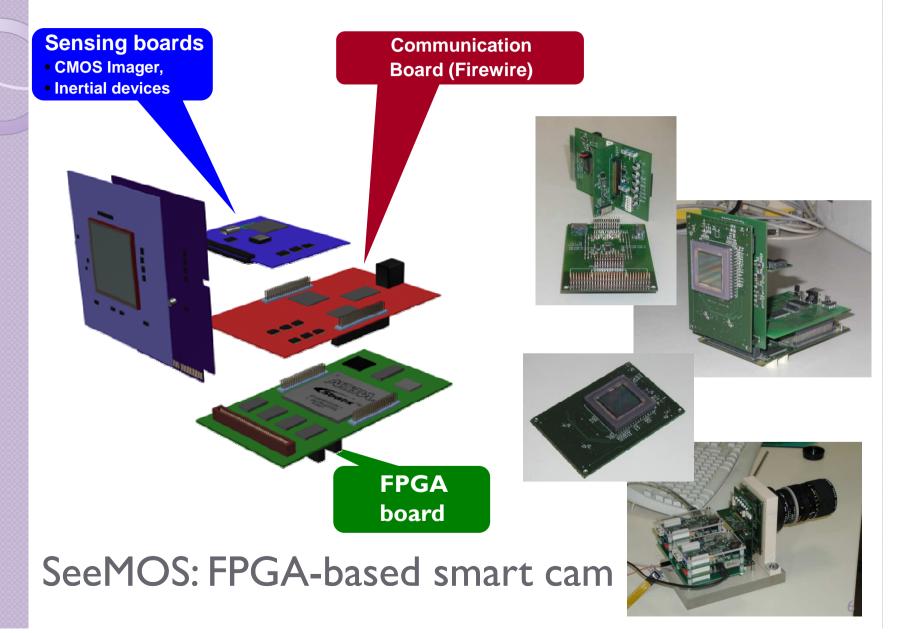

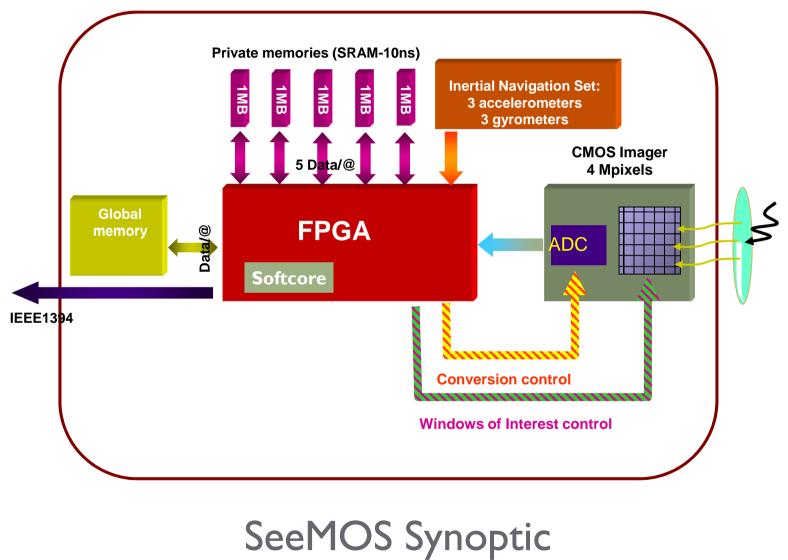

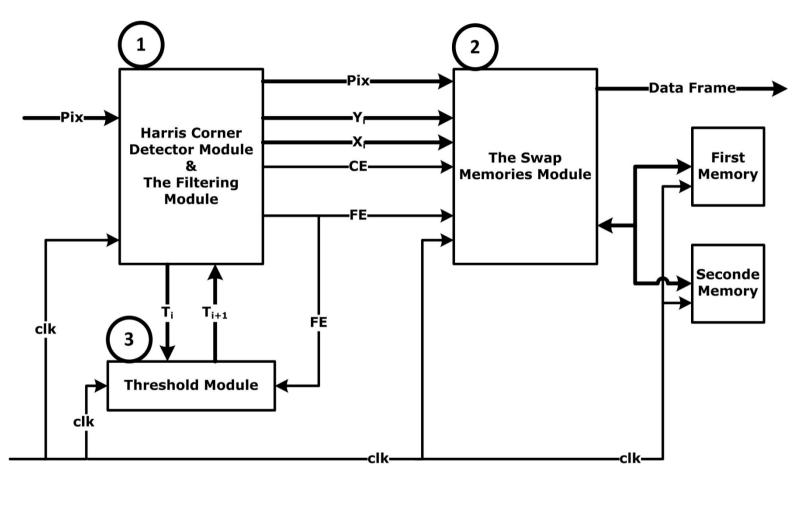

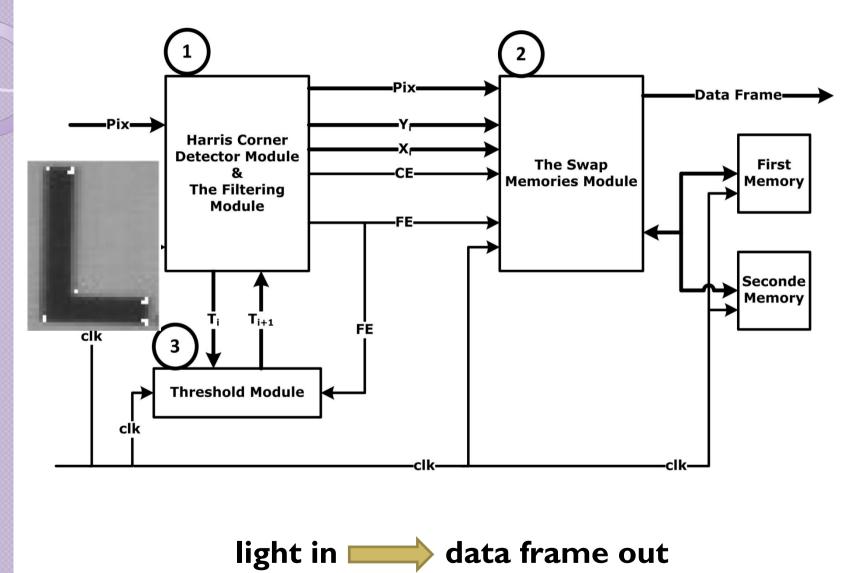

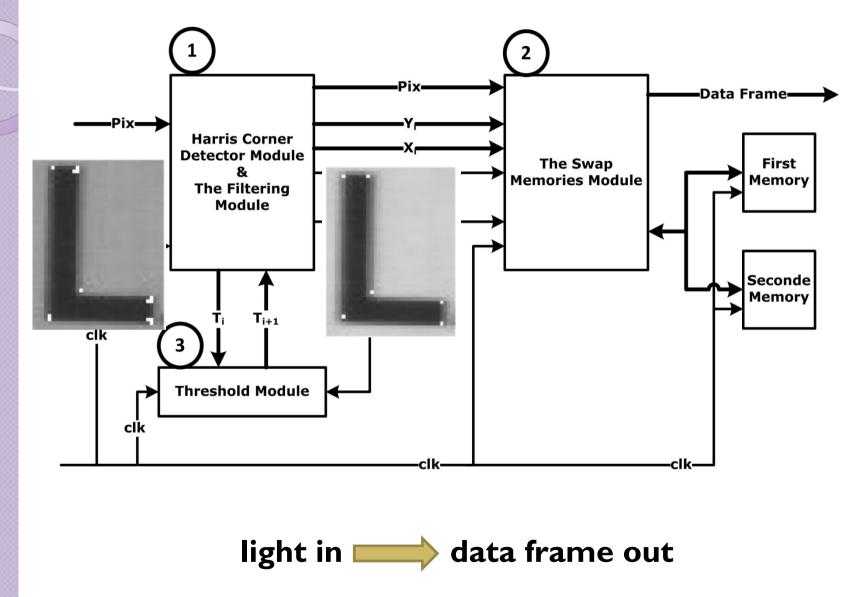

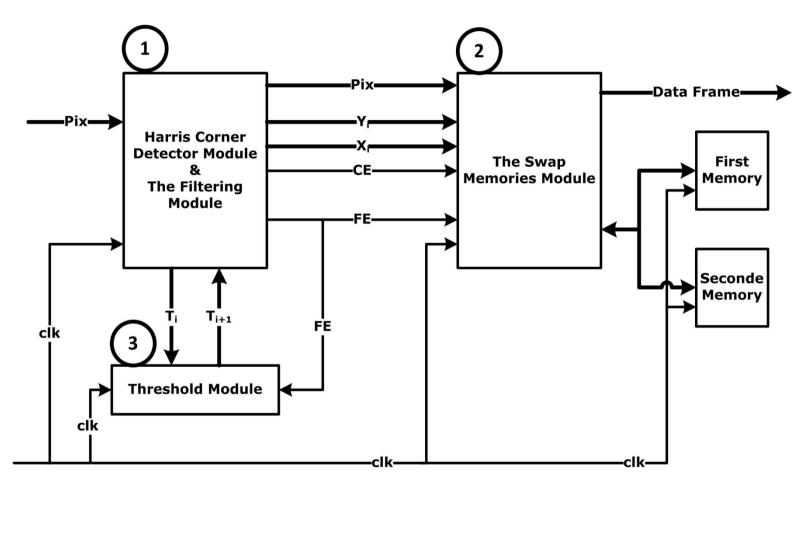

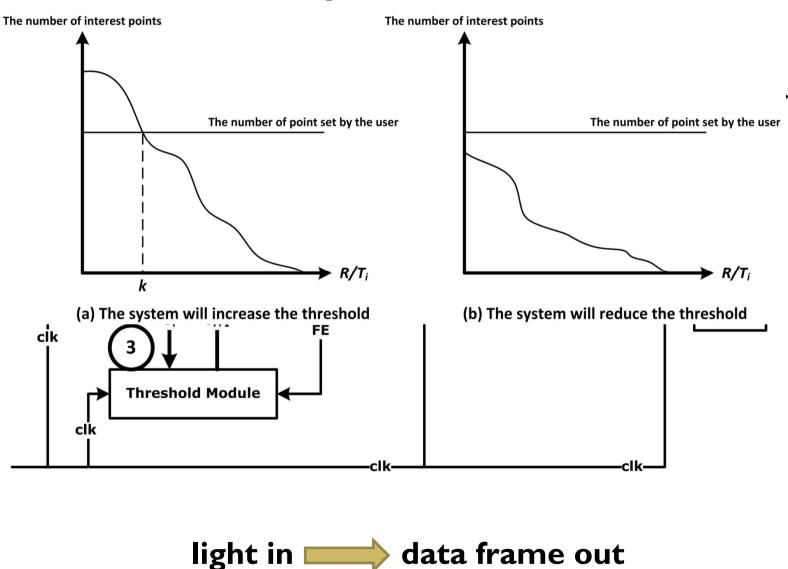

- 3 The hardware implementation,

- 4 The results of the implementation,

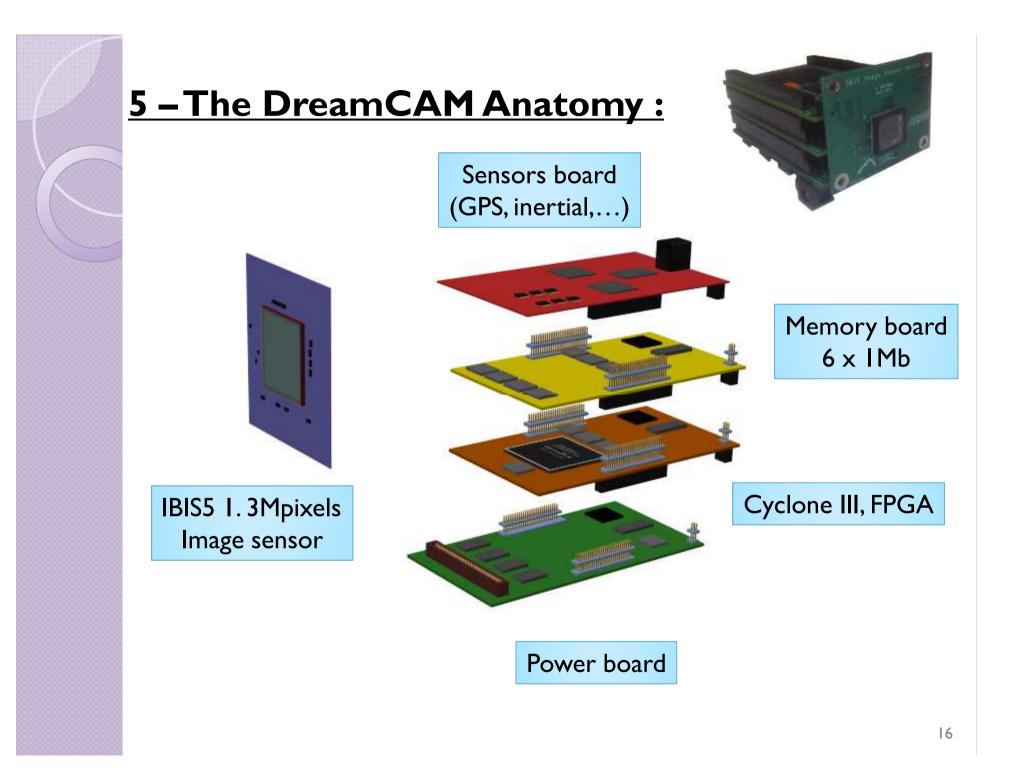

- 5 The DreamCAM,

#### - Feature Extraction :

is used to describe the combination of *feature detector*, and a *feature descriptor*.

#### Feature detector

Harris & Stephen algorithm

#### Feature descriptor

A simple descriptor, which gives for each interest point an intensity patch from the image (its neighbors).

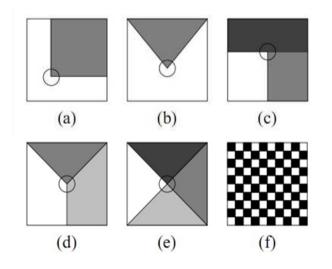

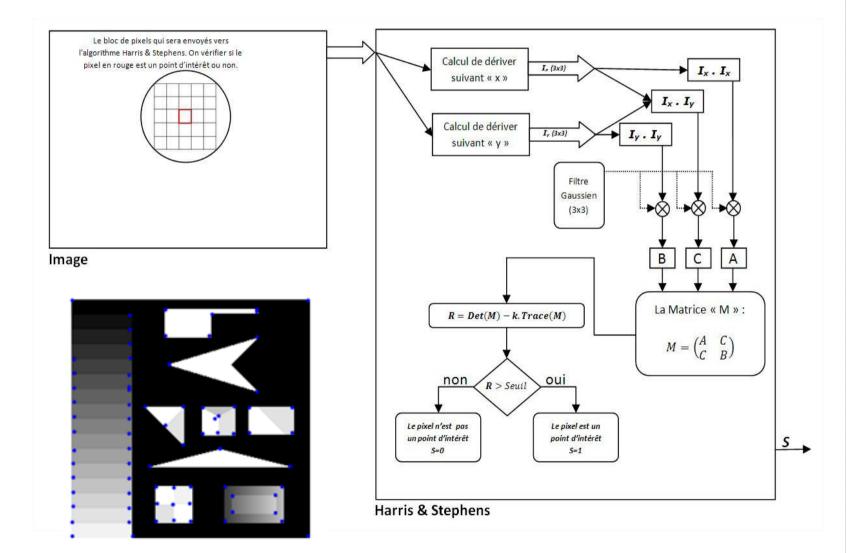

### 2 - Harris & Stephen detector (1988): 1/2

Currently, most of the computer vision algorithm use interest point of type Harris & Stephen as input.

#### Because :

- $\succ$  It is based on simple principal,

- Gives acceptable results

#### 2 - Harris & Stephen detector (1988): 2/2

light in **mathematical** data frame out

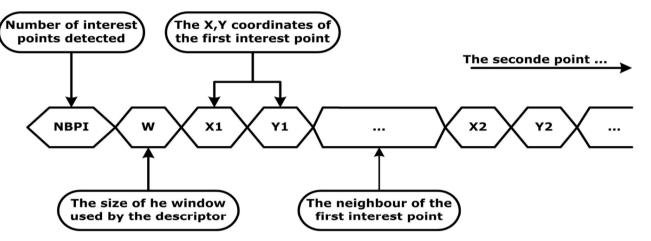

The data frame :

## <u>4 – The results of the implementation : I/2</u>

From the compilation report : (for image 256x256 pixels)

$\succ$  The maximal frequency = 22.52MHz,

➤The FPGA resources used :

| Logic Elements | 11'327 / 57'120       | 20% |

|----------------|-----------------------|-----|

| Memory Bits    | 1'066'376 / 5'215'104 | 20% |

| DSP-block      | 33 / 44               | 23% |

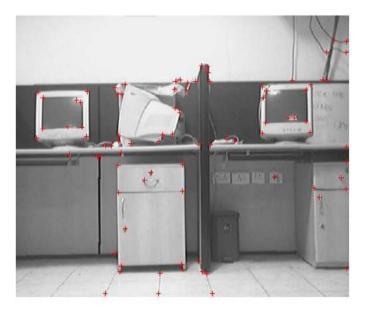

#### 4 – The results of the implementation : 2/2

# Thanks For Your Attention